Link

Offered by the Hebrew University of Jerusalem

Found here - CS curriculums

Resources

- HDL Survival Guide

- The Elements of Computing Systems

- https://en.wikipedia.org/wiki/Endianness

- Online IDE

2024-12-31

- Truth tables, boolean operations

NOT(0 OR (1 AND 1))- Commutative, associative and distributive laws

- De Morgan Law →

NOT(x AND y) = NOT(x) OR NOT (y) x NAND y = NOT(x AND y)NOT x = x NAND xx AND y = NOT( x NAND y)- Gate interface ( what it does ) x implementation ( how it does )

2025-01-03

- Multi-bit buses

- Bus = Bunch of bits

- Handling the input as a single entity

CHIP Add16 {

IN a[16], b[16];

OUT out[16];

PARTS:

...

}2025-01-04

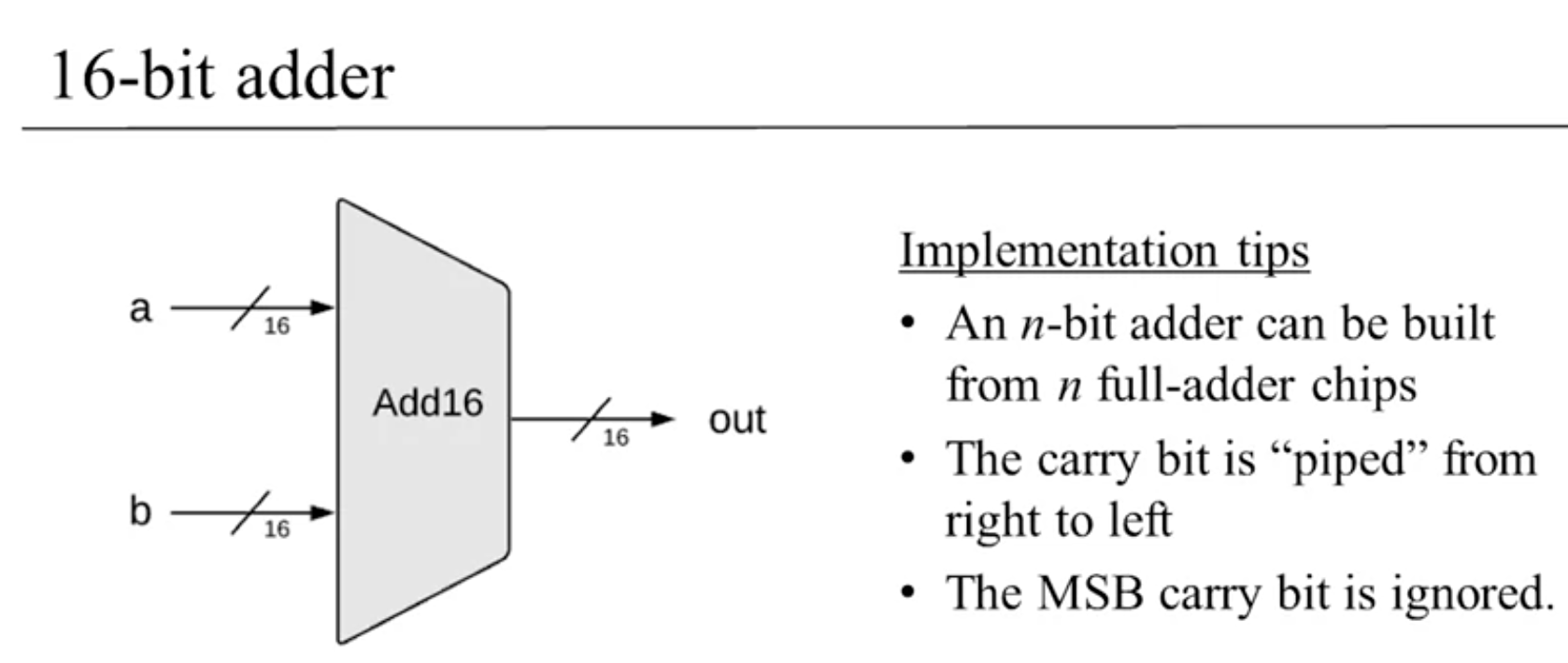

MSB → Most significant bit → a[15]

LSB → Least significant bit → a[0]

Multiplexor (Mux) Gate

- Basically an if gate, the

selinput picks if theaorbinput if being output

Demultiplexor (DMux) Gate - Input

in,seloutputaandb

if (sel == 0)

{a,b}={in,0}

else

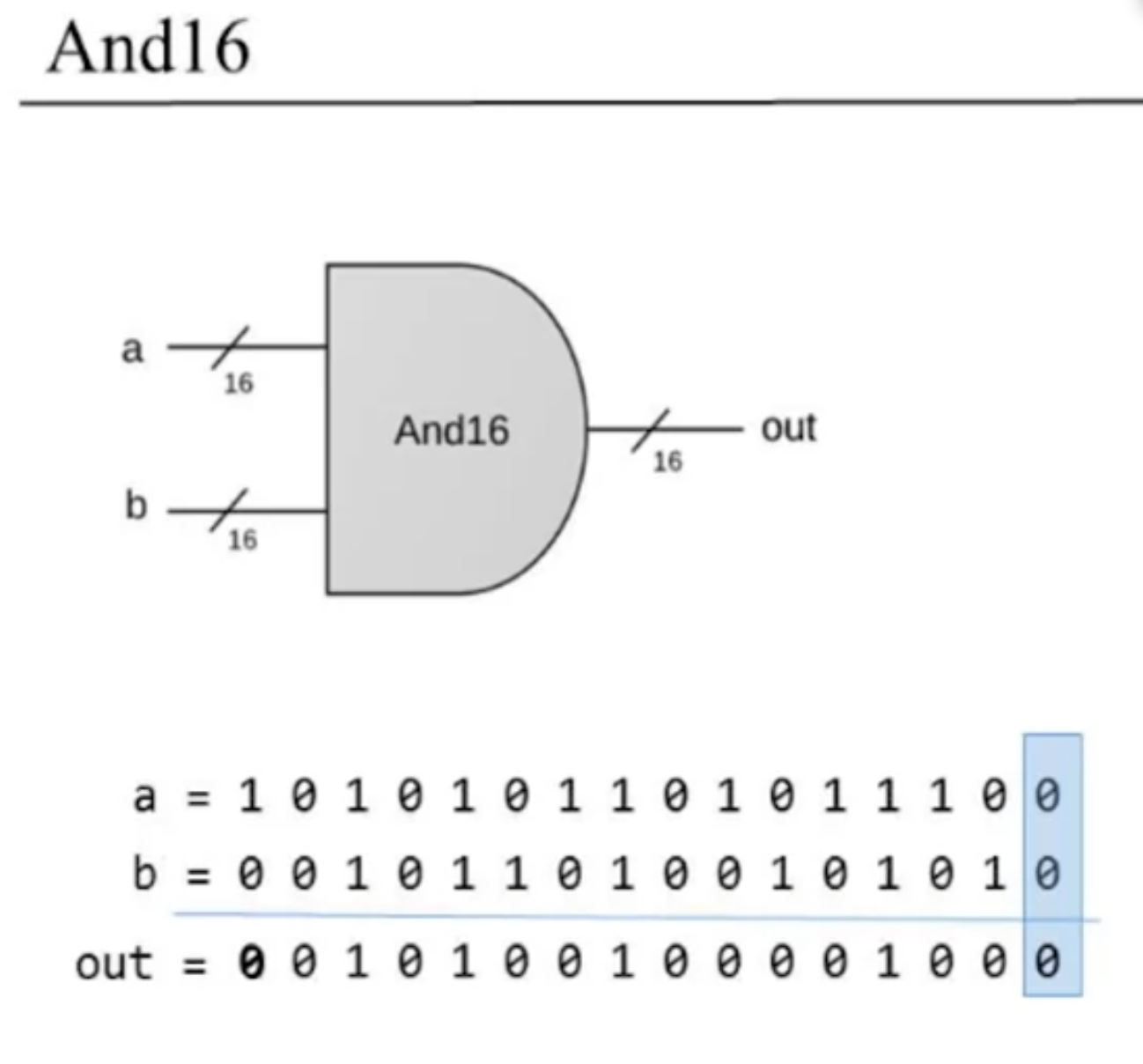

{a,b}={0,in}And16

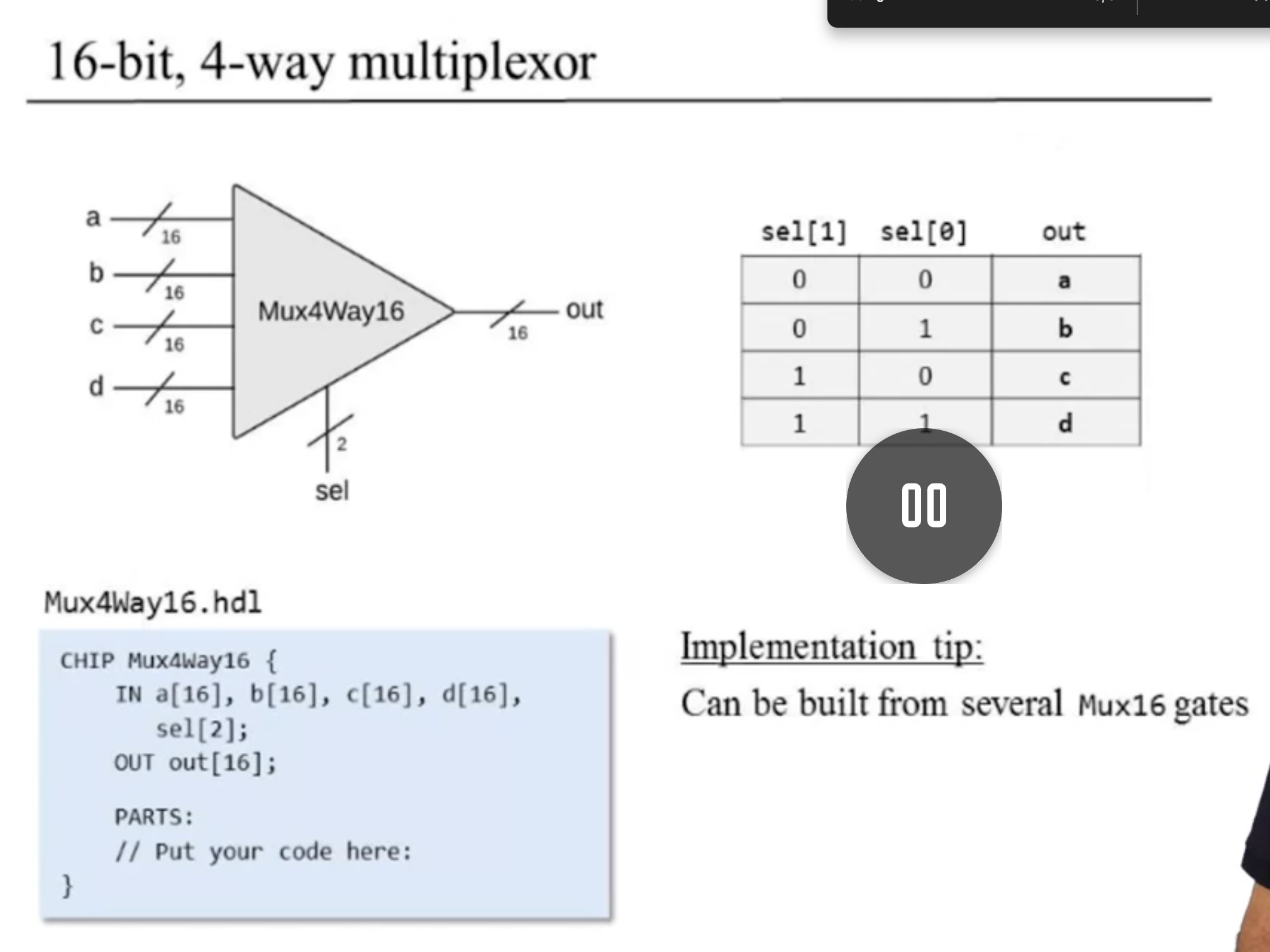

16-bit 4-way mux

2025-01-13

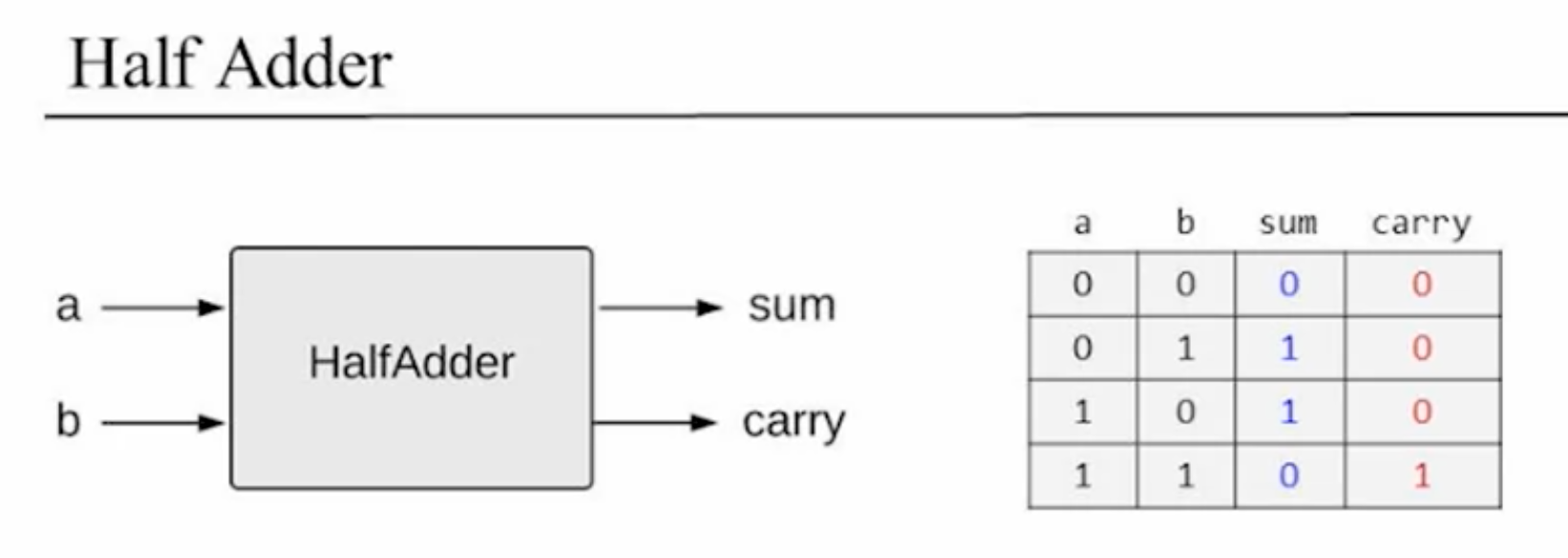

Half Adder

- Sum ~

XOR - Carry ~

AND

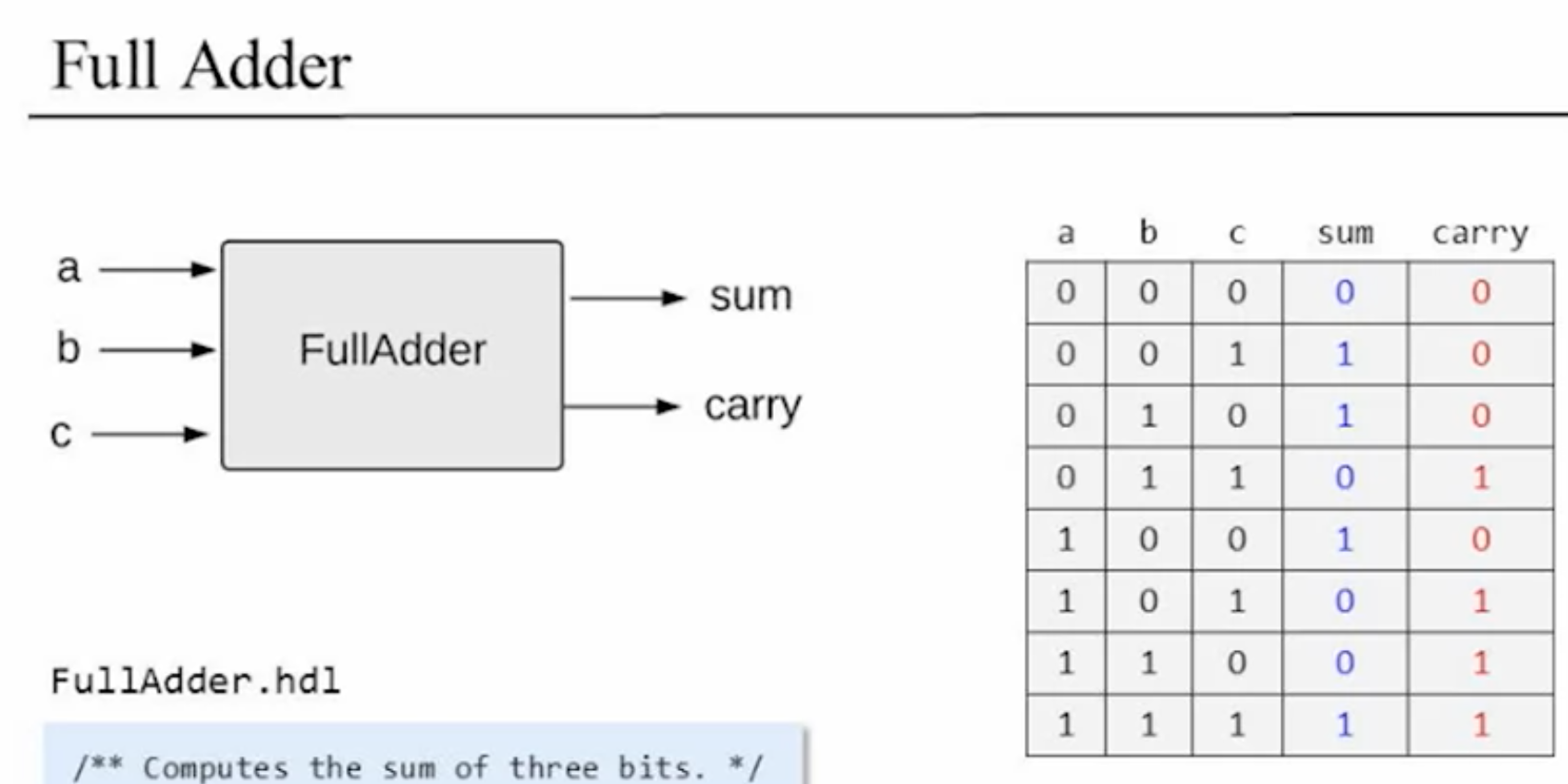

Full Adder

- Two half adders

16-bit Adder

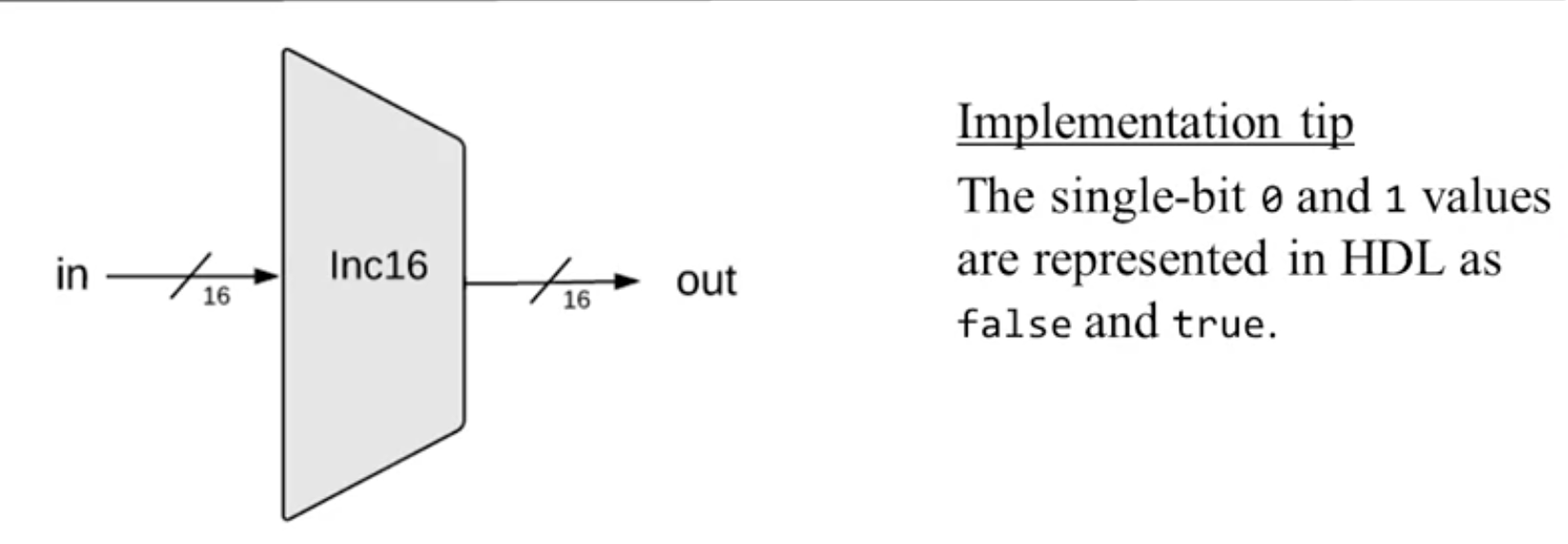

16-bit incrementor

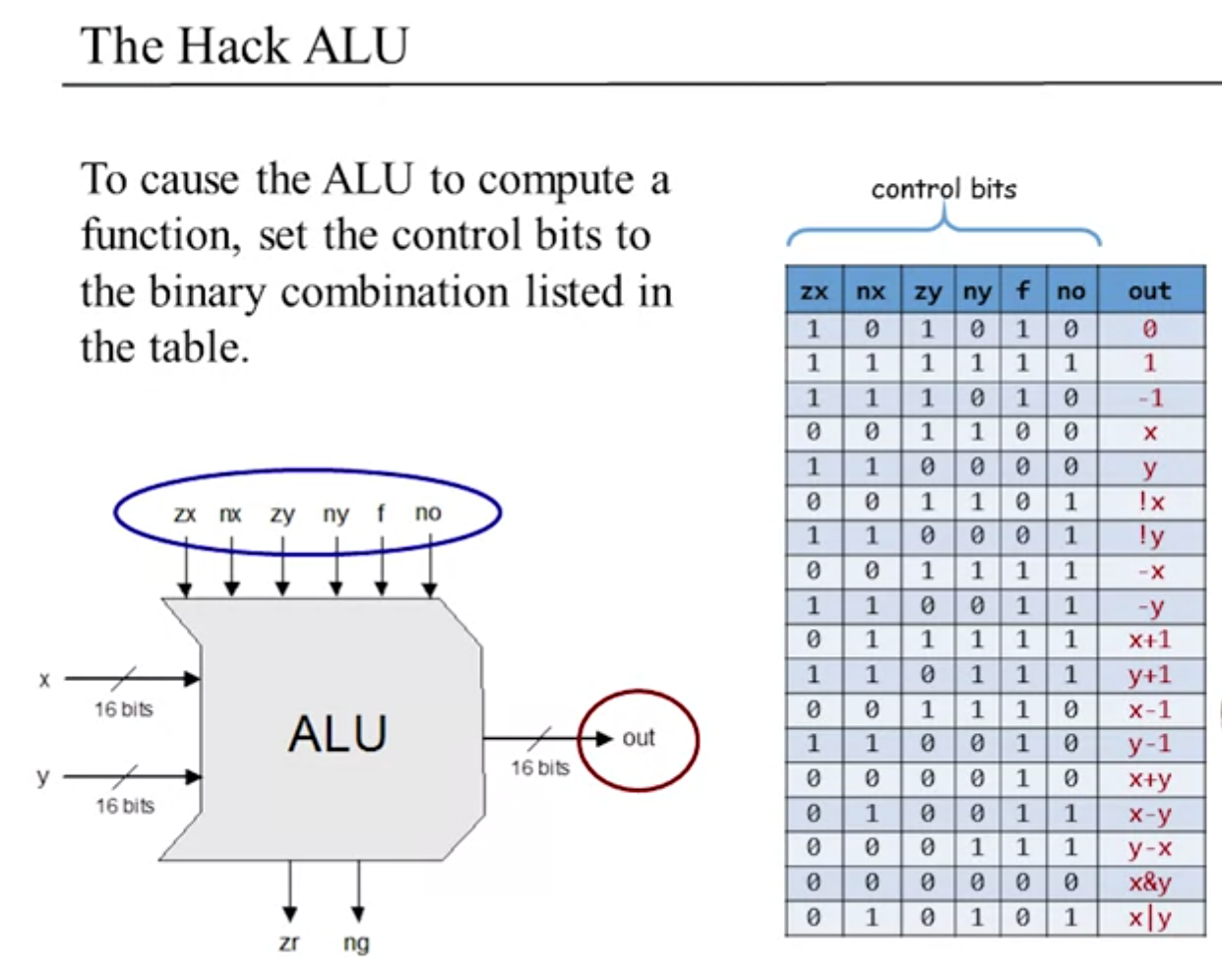

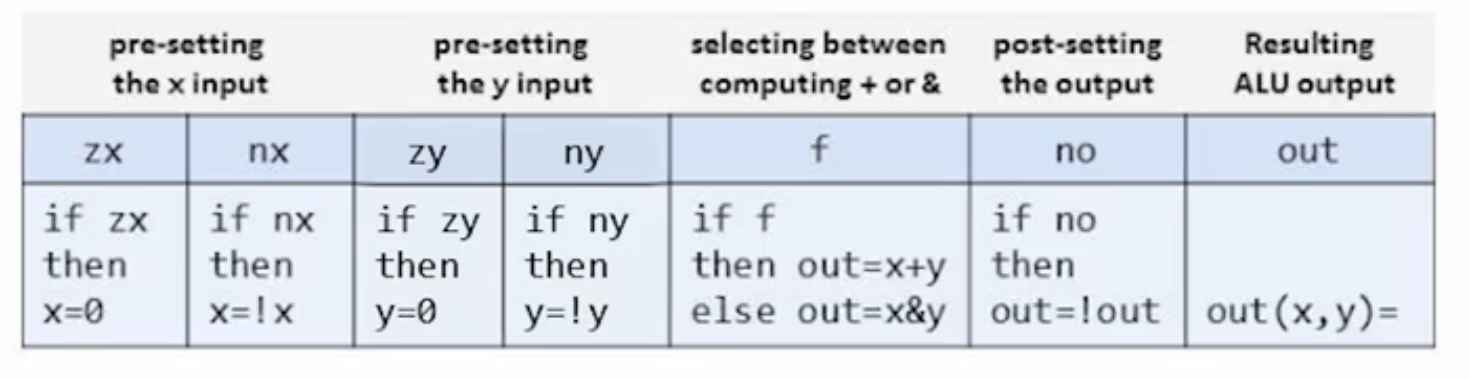

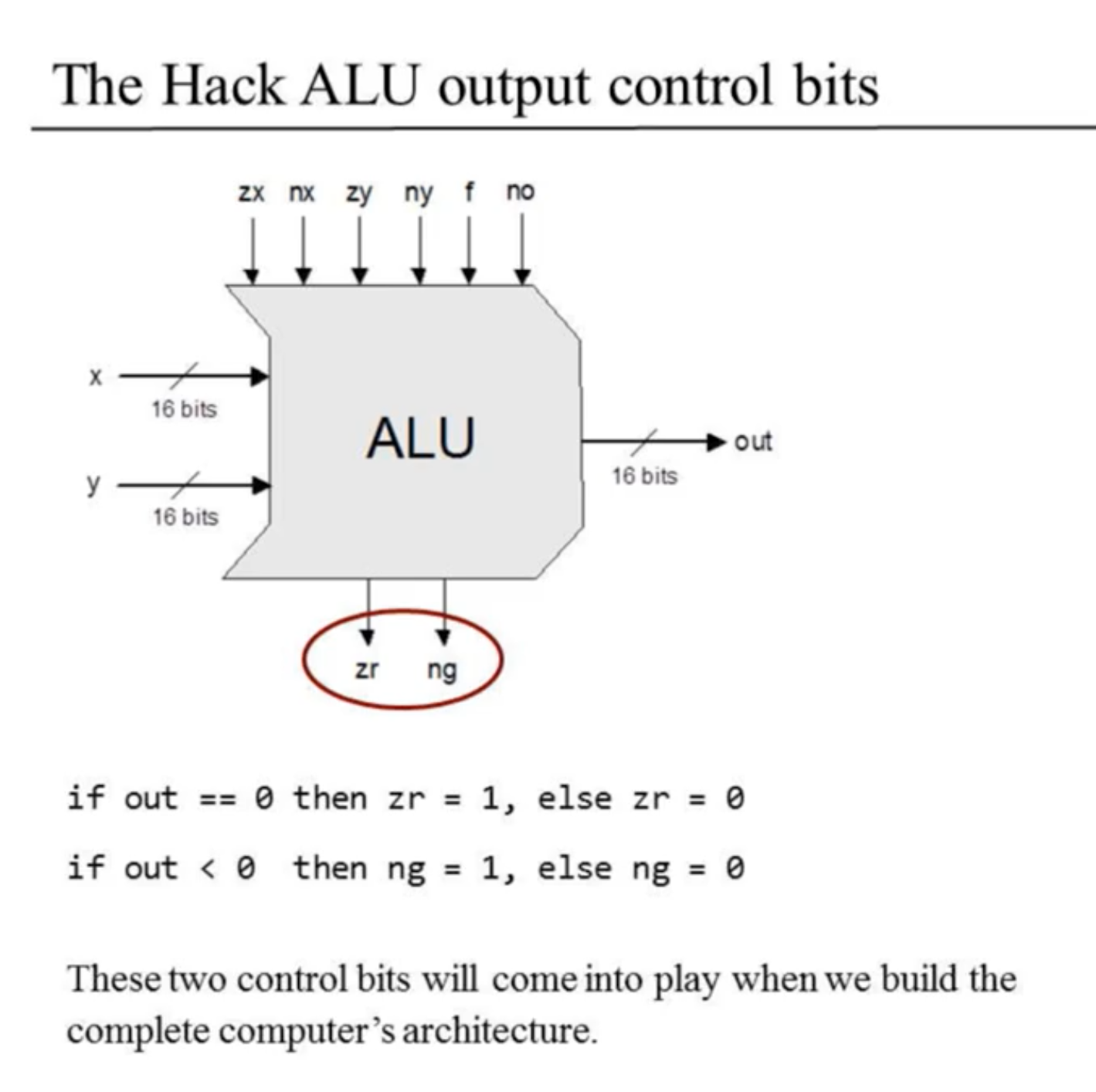

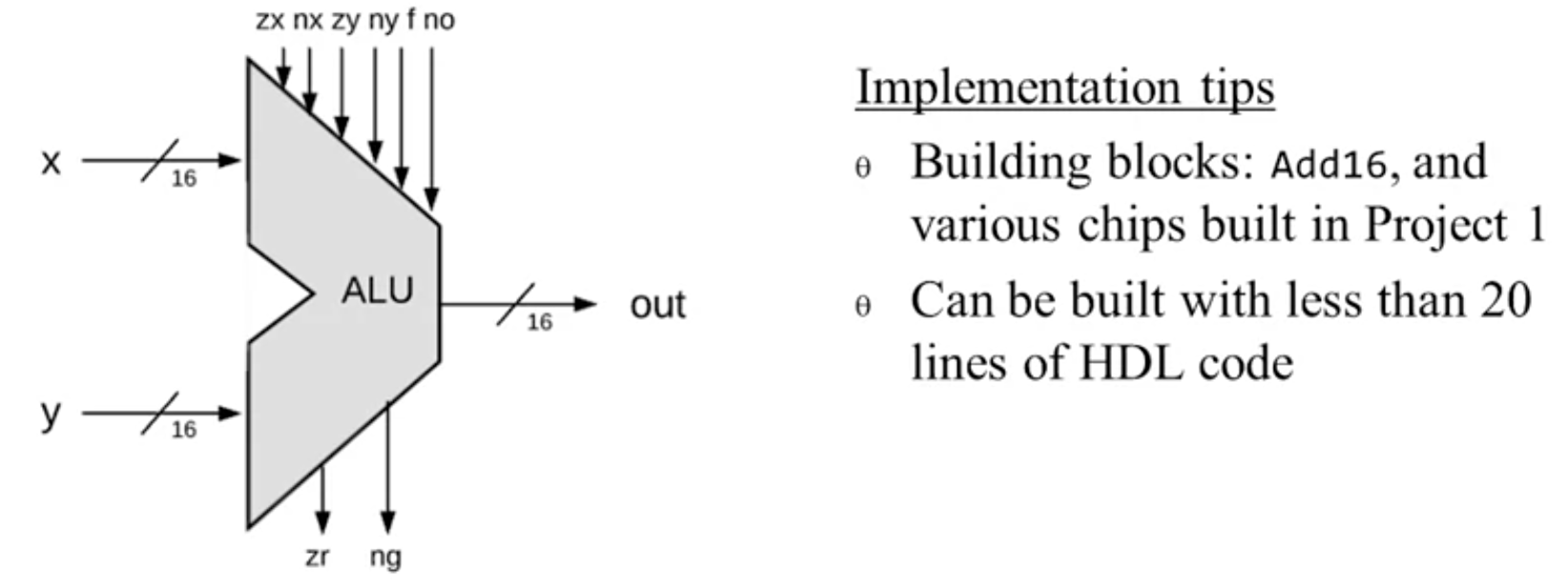

ALU

2025-01-21

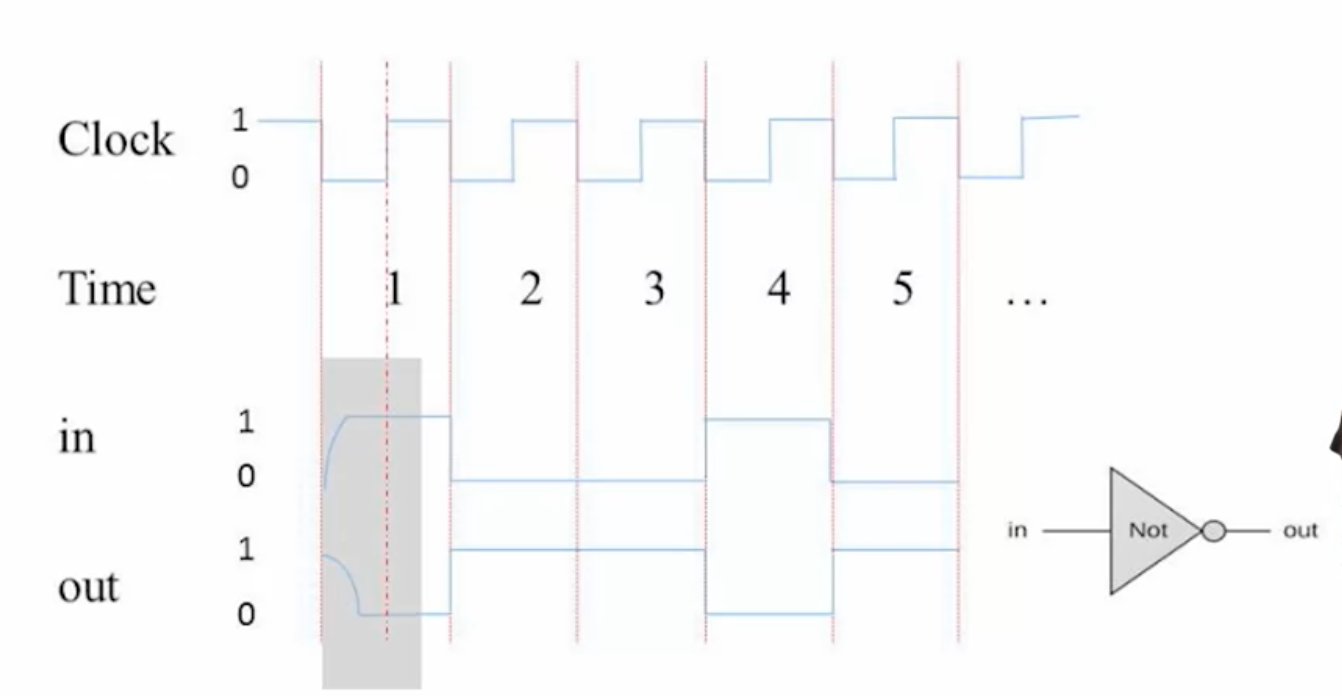

we need an abstraction for dealing with electricity instabilities, like the time it takes for a bit to flip, so we break the continuous time into discrete time and evaluate only the last state, in a clock

Flip Flop (D Flip Flop - DFF)

Simply a delayed version of the bit, will represent the input in the previous state , in[t-1]

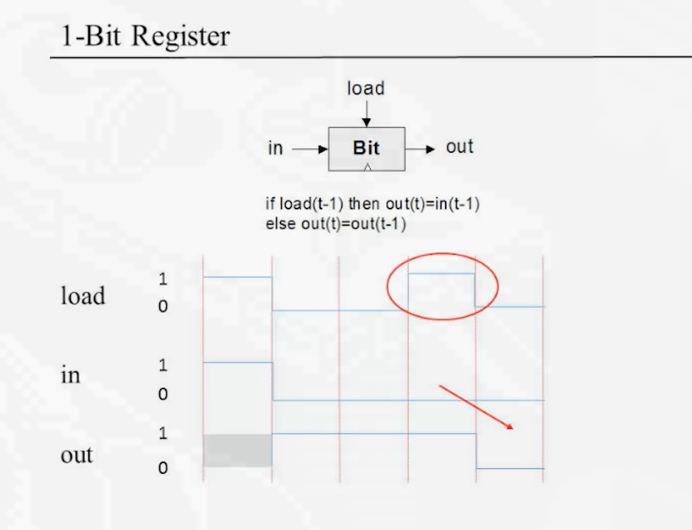

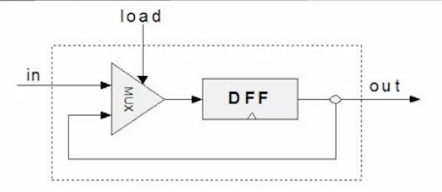

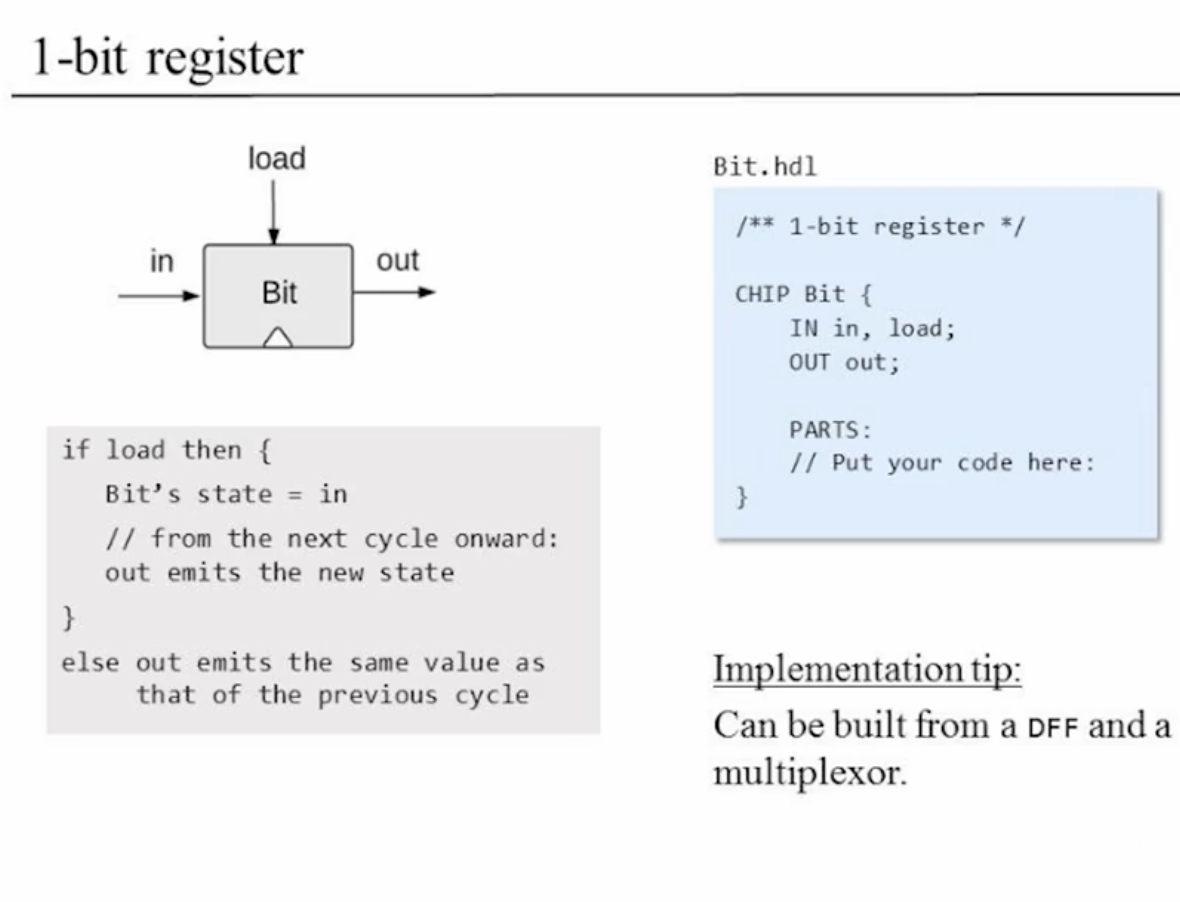

1-bit Register

2025-01-29

- Main memory

- RAM

- Secondary memory

- Disks

- Volatile / non-volatile

- Volatile → looses data when powered off (RAM)

1-bit Register

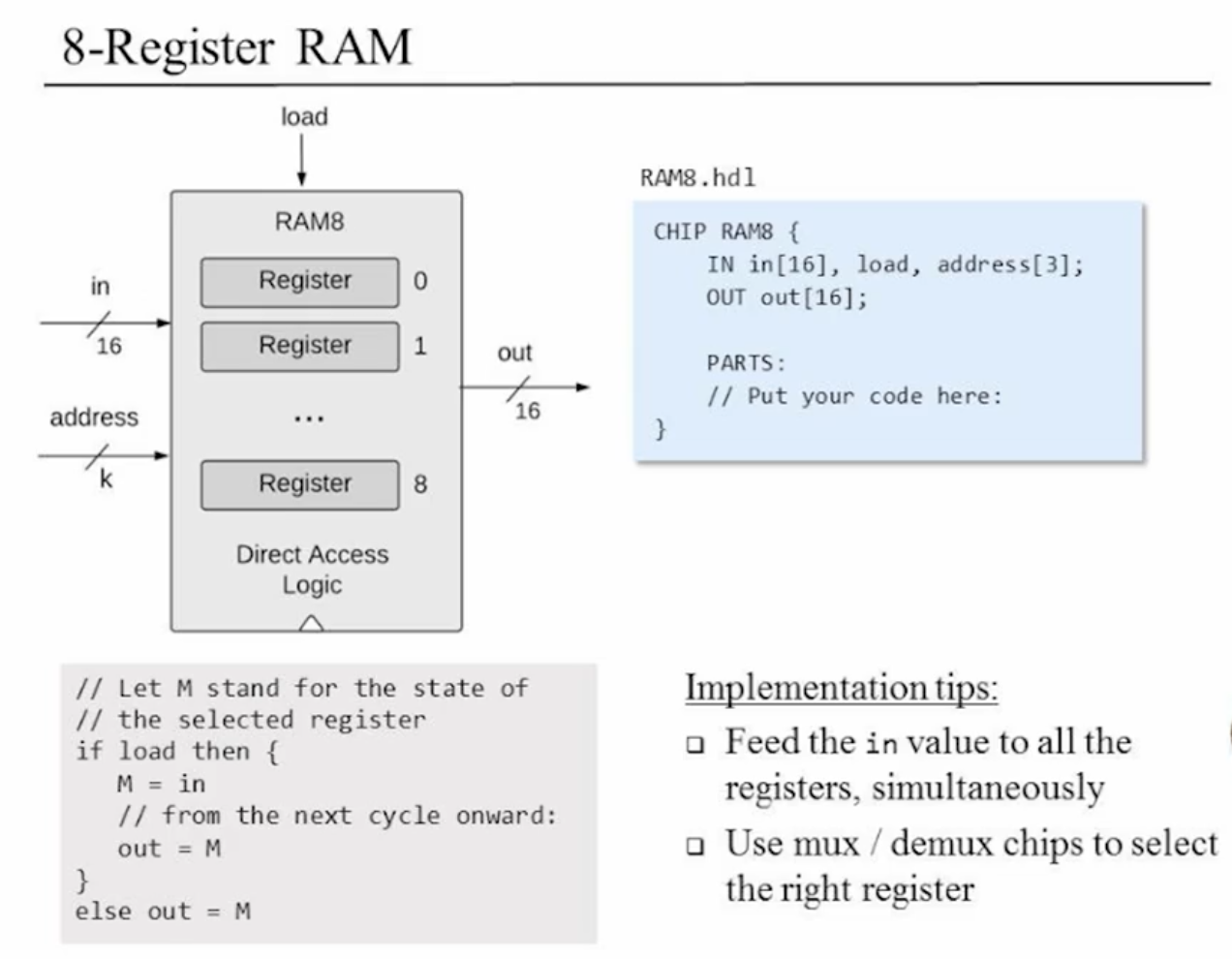

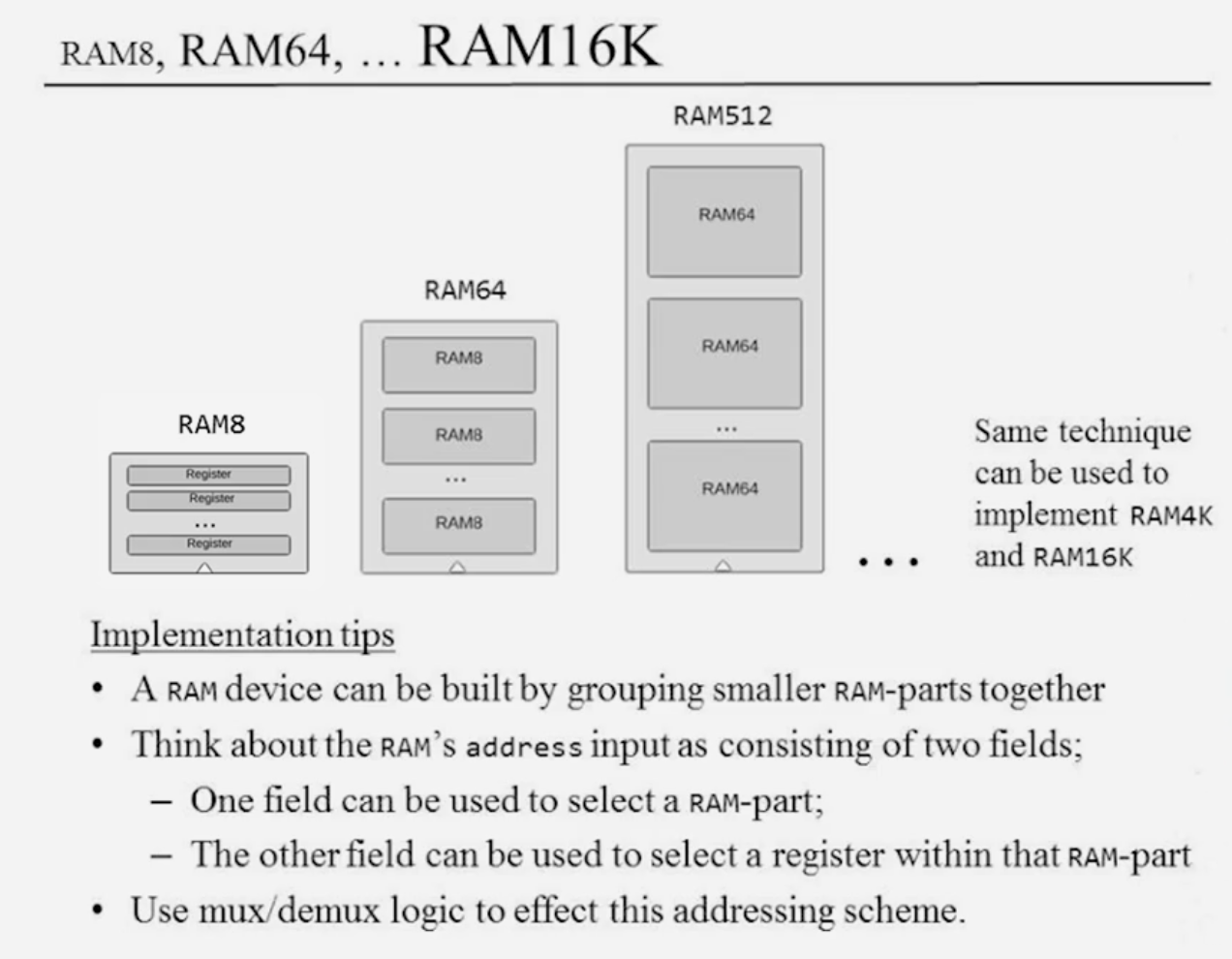

8-Register RAM

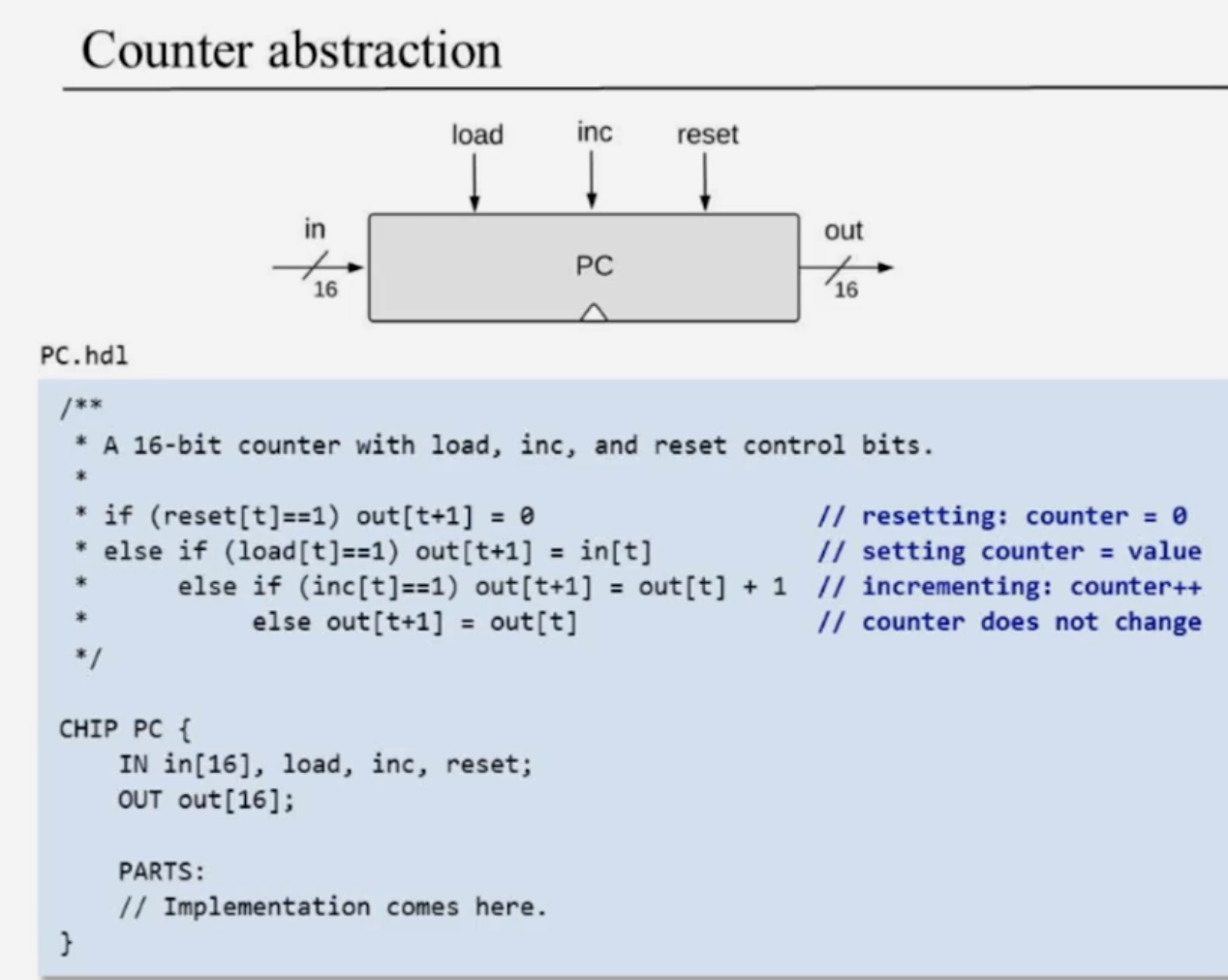

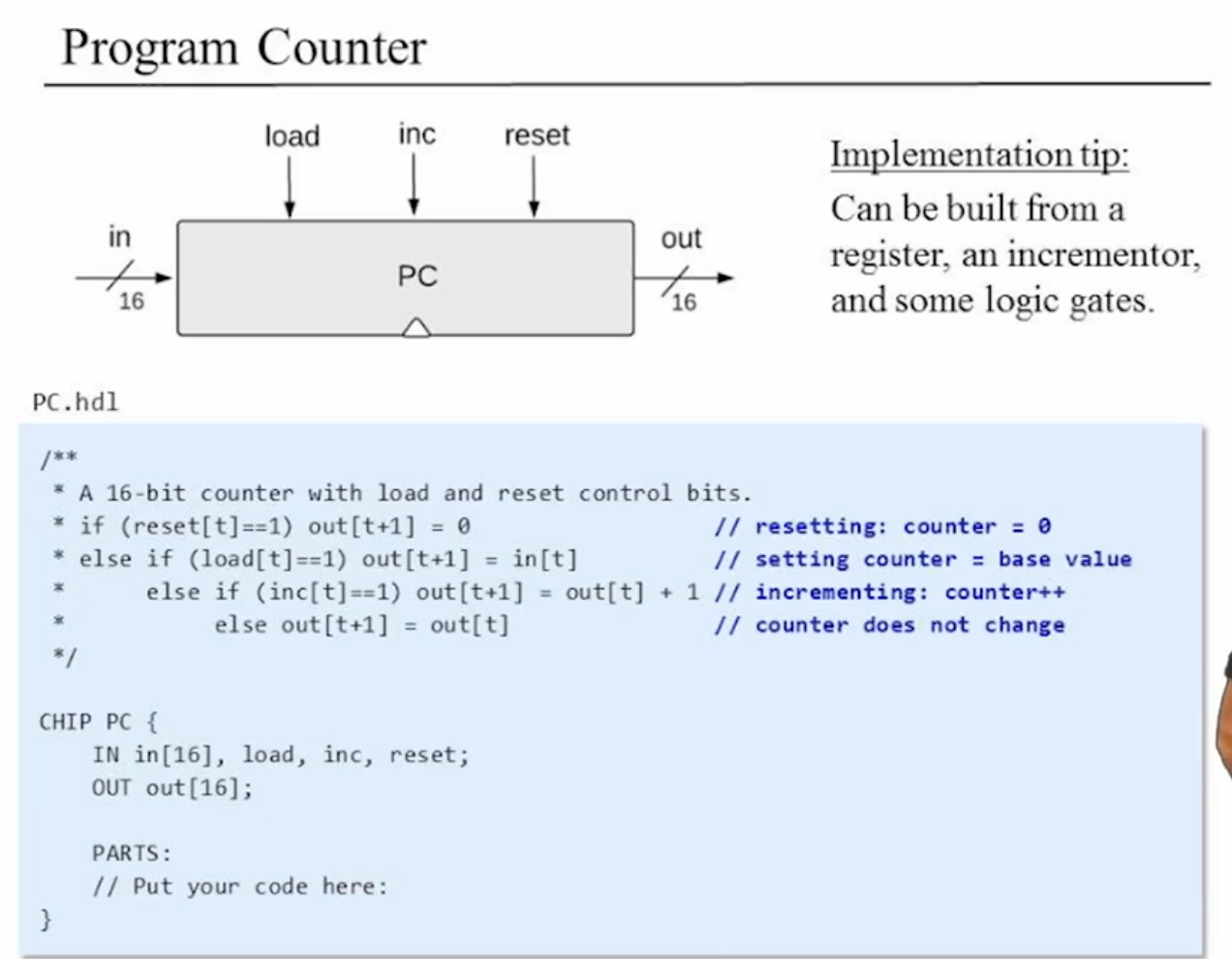

Counters

- fetch first instruction

- fetch next instruction

- go to instruction